In 2009, gate oxide thickness reached just 2.2Å, according to the ITRS. This tiny size shows how important gate dielectric stacks are in modern semiconductors. Picking the right materials for these stacks is crucial as we make CMOS technology even smaller.

Moore’s Law pushes the semiconductor industry to shrink device sizes. This scaling needs thinner gate dielectrics, measured by equivalent oxide thickness (EOT). High-k materials like hafnium-based oxides are replacing traditional silicon dioxide gate dielectrics.

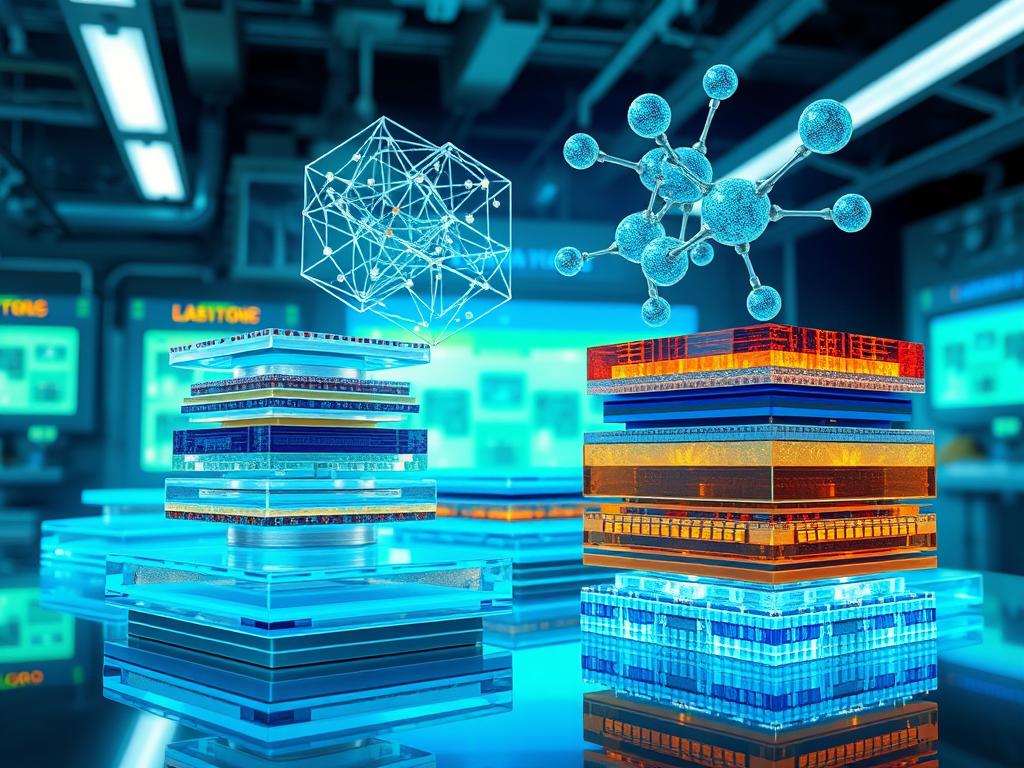

The move to high-k materials and metal gate electrodes (HKMG) is a big step in chip making. These new gate stacks usually have three parts: a silicon oxide layer, a high-k dielectric, and a metal gate electrode. This setup allows for smaller sizes while keeping the right electrical properties.

Gate dielectric stacks are key to the future of semiconductor devices. They impact everything from phones to cars. The tiny components have a huge effect beyond just silicon chips.

Understanding Gate Dielectric Stacks and Their Function

Gate dielectric stacks are key parts of modern semiconductor devices. These multi-layered structures control current flow and boost semiconductor performance. They’re vital in the fast-changing world of microelectronics.

What Are Gate Dielectric Stacks?

Gate dielectric stacks are made of multiple layers of carefully chosen materials. They usually have an interfacial layer, a high-k dielectric layer, and a metal gate electrode.

This mix allows better control over the gate dielectric function. It also helps to reduce leakage current in the device.

Importance in Semiconductor Devices

Gate dielectric stacks are crucial for semiconductor devices. They maintain control over the channel and reduce leakage current.

These stacks also allow for MOSFET scaling, which helps make devices smaller. They improve the overall efficiency and performance of semiconductor devices.

- Maintaining electrostatic control over the channel

- Reducing leakage current

- Enabling MOSFET scaling for continued device miniaturization

- Improving overall device efficiency and performance

Impact on Device Performance

Gate dielectric stacks greatly affect device performance. They influence key factors like equivalent oxide thickness (EOT) and gate capacitance.

Engineers use a formula to optimize gate stack designs. The total EOT of a high-k metal gate stack is:

EOT = EOTIL + EOTHK

EOTIL and EOTHK are from the interfacial layer and high-k layer. This formula helps create better-performing devices.

Recent tests show promise for even smaller devices. Gate stacks with high dielectrics below 2nm effective oxide thickness are now possible.

This breakthrough opens doors for more advanced MOSFET scaling. It also pushes semiconductor technology forward in exciting new ways.

Key Materials Used in Gate Dielectric Stacks

Gate dielectric stacks are vital in semiconductor devices. They’ve evolved to meet modern electronics demands. Let’s explore key materials used in these stacks and their impact on performance.

Silicon Dioxide: The Traditional Choice

SiO2 has been the main gate dielectric for decades. It offers a stable interface with silicon and excellent insulation properties. However, SiO2 reaches its limits in sub-70 nm CMOS technology.

The gate leakage current through SiO2 can exceed 1 A/cm2 at 1 V. This issue has led to the search for better alternatives.

High-k Dielectrics: Advantages and Trade-offs

High-k dielectrics solve SiO2’s limitations. Materials like HfO2 have higher dielectric constants. This allows for thicker layers that reduce leakage current while maintaining capacitance.

Intel has used high-k/metal gate stacks in their second-generation chips. These stacks work even for advanced FINFET structures.

| Material | Dielectric Constant | Advantages |

|---|---|---|

| SiO2 | 3.9 | Excellent interface, well-understood |

| HfO2 | ~20 | Lower leakage, better scaling |

| ZrO2 | ~25 | High dielectric constant, thermal stability |

Emerging Materials: What’s on the Horizon?

Gate stack engineering keeps evolving with new materials. La-based materials and rare earth oxides show promise for future devices. These options aim to outperform current high-k dielectrics.

They offer higher dielectric constants and improved device-level performance. These materials may unlock new levels of efficiency and miniaturization in advanced semiconductor fabrication.

The shift from SiO2 to high-k dielectrics shows ongoing innovation in semiconductors. As devices shrink, gate dielectric materials remain crucial for optimal performance and efficiency.

The Role of Thickness in Dielectric Stacks

Dielectric stack thickness greatly affects semiconductor device performance. Engineers face challenges in balancing performance and reliability as EOT scaling advances. This push for thinner layers continues to drive technological progress.

Optimal Thickness for Performance

Gate dielectric thickness has changed dramatically over time. In the 1970s, it ranged from 50-100 nm. Now, high-performance microprocessors use dielectrics as thin as 1.1-1.6 nm.

This reduction aims to boost device speed and efficiency. However, it also brings new challenges to overcome.

The perfect gate dielectric should have low fixed charge and interface states. These qualities help maintain device reliability and reduce gate leakage. As we reach the limits of traditional materials like silicon dioxide, new solutions become necessary.

Trade-offs Between Size and Dielectric Constant

Modern gate stack design centers on balancing size and dielectric constant. High-k materials allow for thicker layers while maintaining or reducing EOT. This approach helps solve issues like gate leakage and mobility degradation.

| Material | Dielectric Constant | Typical Thickness | Challenges |

|---|---|---|---|

| SiO2 | 3.9 | 1.5 nm | Direct tunneling, breakdown |

| HfO2 | 25 | 2-3 nm | Mobility degradation, charge trapping |

| Al2O3 | 9 | 2-4 nm | Lower k than HfO2, interfacial layer growth |

Engineers must carefully consider high-k layer thickness and interfacial layer properties. A thick HfO2 layer can cause mobility degradation. An overly thin interfacial layer may harm reliability.

Balancing these factors is crucial for optimal device performance. This balance becomes even more important as EOT scaling becomes more aggressive.

Technological Advances in Gate Dielectric Stacks

Gate dielectric stack technology has made incredible strides in the semiconductor industry. Intel’s 2007 introduction of high-k dielectrics and metal gates sparked a wave of innovations. These advancements have greatly improved chip performance and reliability.

Innovations in Material Science

Material science has transformed gate dielectric stacks. High-κ dielectrics now match SiO2-based dielectrics with an equivalent oxide thickness of about 1 nm. Scientists are exploring dielectrics with κ values over 26 and barrier heights around 5.0 eV.

These efforts aim to achieve the ambitious 0.5-nm EOT target. Such advancements could revolutionize semiconductor performance and efficiency.

The Impact of Nanotechnology

Nanotechnology has enabled precise control in fabrication processes. Atomic layer deposition and interfacial layer engineering are crucial for advanced gate stacks. These techniques allow for nanoscale material manipulation, boosting performance and reliability.

Future Trends in Semiconductor Fabrication

Semiconductor fabrication’s future looks bright. Epitaxial growth of high-k dielectrics and nanostructured dielectrics are key research areas. These advancements aim to simplify manufacturing while boosting chip performance.

The industry is working to integrate over 10 billion transistors per circuit. At the same time, they’re striving to reduce power dissipation.

Scaling gate stacks to smaller dimensions remains a priority. This challenge requires innovative material selection and processing techniques. The goal is to maintain reliability and performance at the nanoscale level.

Practical Applications Across Industries

Gate dielectric stacks revolutionize electronic device design and manufacturing. These advanced materials impact semiconductor manufacturing, consumer electronics, and automotive and aerospace sectors. Their role is crucial in various industries.

Semiconductor Manufacturing

Gate dielectric stacks are vital for producing high-performance logic devices and memory components. CMOS technology relies on these stacks for smaller, faster processors. High-k dielectrics enable Moore’s Law, increasing transistor density and improving performance.

Consumer Electronics

Gate dielectric technology advances benefit the consumer electronics industry. Mobile devices use these materials to boost battery life and processing power. IoT devices also use gate dielectric stacks for better energy efficiency and connectivity.

Automotive and Aerospace Applications

Automotive electronics use gate dielectric stacks for reliable, efficient control units and sensors. These components are essential for electric vehicles and driver assistance systems. Aerospace applications use high-k dielectric stacks in radiation-hardened and high-temperature semiconductor devices.

| Industry | Application | Benefits |

|---|---|---|

| Semiconductor | Logic devices, SRAM | Increased transistor density, improved performance |

| Consumer Electronics | Smartphones, IoT devices | Enhanced battery life, faster processing |

| Automotive | Electric vehicles, ADAS | Improved reliability, efficient power management |

| Aerospace | Radiation-hardened electronics | Enhanced durability in extreme conditions |

Gate dielectric stacks are essential in modern technology. They power everyday devices and enable cutting-edge innovations. These materials shape the future of electronics across multiple industries.

From smartphones to spacecraft, gate dielectric stacks drive progress. They continue to improve performance in high-performance computing and beyond. Their impact on technology is undeniable and far-reaching.

Challenges and Considerations in Material Selection

Choosing gate dielectric stack materials is a complex task. The semiconductor industry faces hurdles in balancing performance, reliability, and cost. Let’s examine the key factors influencing material selection for these crucial components.

Thermal Stability and Reliability

Thermal stability is a primary concern in material selection. High temperatures can affect device performance by changing material properties. Reliability testing ensures gate dielectric stacks withstand manufacturing and operation stresses.

La-based higher-κ materials show promise for aggressive EOT scaling. However, their long-term stability requires thorough evaluation before implementation.

Compatibility with Existing Processes

New materials must integrate with current CMOS fabrication techniques. This includes controlling the effective workfunction for both NMOS and PMOS devices.

Materials like La-Al-O have shown EWF control capabilities. These range from the Silicon Conduction Band Minimum to near the Silicon mid-gap.

Cost Implications of Material Choices

The semiconductor industry invested 82 billion USD in materials and equipment in 2014. This led to 336 billion USD in semiconductor sales, highlighting the importance of cost-effective scaling.

Material choices affect raw material availability and deposition equipment needs. They can also change the overall manufacturing process. As devices shrink, finding materials that maintain performance while reducing costs remains challenging.