Vertical nanowire transistors could revolutionize the semiconductor industry. They have the potential to increase chip density by up to 100 times. These innovative devices are set to transform electronics as we know them.

Vertical nanowires are a major advancement in semiconductor technology. They offer a solution to overcome the limits of traditional planar transistors. By using the vertical dimension, these structures allow for efficient 3D integration.

The unique design of vertical nanowire transistors provides better control over electron flow. This results in improved performance and lower power use. The breakthrough in 3D integration paves the way for new compact, fast devices.

Vertical nanowires hold immense potential for shaping the future of electronics. We’ll explore their physics, fabrication techniques, and possible applications. This cutting-edge technology is set to redefine semiconductor innovation.

Nanowire Physics

Vertical nanowire transistors are changing semiconductor technology. These tiny structures have unique physical properties. The nanowire’s aspect ratio greatly affects its electrical characteristics.

Quantum Effects

Quantum confinement becomes important at the nanoscale. Electrons behave differently in small spaces, creating discrete energy levels. This changes the bandgap and optical properties of nanowires.

These changes open up new possibilities for device design. Engineers can now create more efficient and powerful transistors.

Transport Mechanisms

Carrier transport in nanowires is unique. The one-dimensional nature allows for ballistic transport with minimal electron scattering. This makes nanowire transistors faster and more efficient.

High-performance applications benefit greatly from these properties. Nanowire transistors are ideal for advanced computing and communication systems.

Surface States

Nanowires have a large surface-to-volume ratio. This makes surface states very important. These states can trap carriers and affect device performance.

Engineers must carefully manage surface properties. Proper management ensures optimal nanowire transistor operation.

| Property | Impact on Nanowire Transistors |

|---|---|

| Quantum Confinement | Altered bandgap, enhanced optical properties |

| Ballistic Transport | Improved speed, reduced power consumption |

| Surface States | Potential carrier trapping, requires careful management |

These physical phenomena are key to vertical nanowire transistors. They help unlock the full potential of these devices. Ongoing research will lead to more innovations in this field.

Fabrication Technology

Vertical nanowire transistors require advanced fabrication methods. These techniques combine precision and innovation for high-performance 3D devices. Let’s explore the key aspects of this technology.

Growth Methods

Vapor-liquid-solid growth is a primary method for nanowire fabrication. It forms nanowires from a gaseous precursor using metal catalysts. This process creates controlled structures with excellent electrical properties.

Nanoimprint lithography offers another approach to nanowire creation. It uses physical deformation of resist materials for nanoscale patterns. This cost-effective technique allows large-scale production of uniform nanowire arrays.

Integration Process

Integrating nanowires into devices requires careful planning. Engineers must consider material compatibility and electrical connections. The process becomes more complex with more nanowires and device layers.

Maintaining consistent electrical properties across nanowires is a key challenge. This requires precise control over growth conditions and post-growth processing steps.

3D Assembly

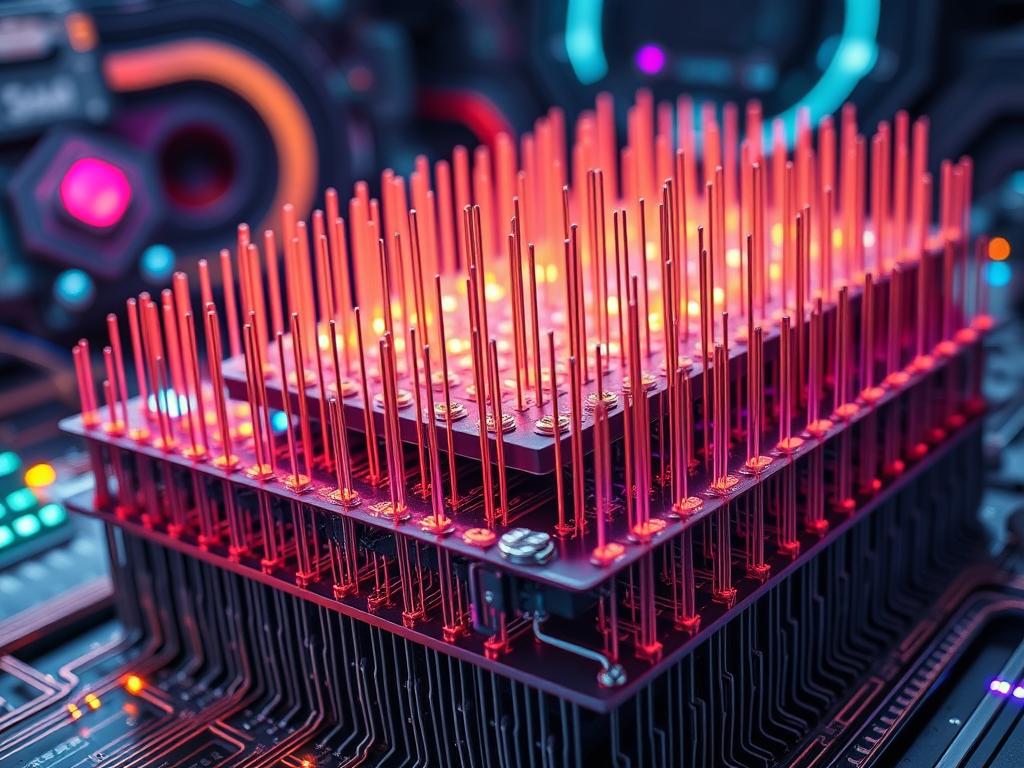

3D assembly of nanowire transistors goes beyond traditional fabrication methods. It involves stacking multiple layers of nanowires for dense, high-performance circuits. This approach maximizes chip space and boosts overall performance.

Advanced techniques like vertical integration allow for interconnected nanowire layers. The result is a compact, powerful device that outperforms planar alternatives.

“3D nanowire assembly represents a paradigm shift in semiconductor fabrication, offering unprecedented device density and performance.”

Fabrication technology continues to evolve rapidly. We’ll see more innovative approaches to nanowire transistor production. These advancements will drive the next generation of efficient electronic devices.

Device Architecture

Vertical nanowire transistors revolutionize semiconductor design. Their unique structure tackles challenges faced by traditional planar devices. These transistors boast key components that set them apart.

Gate Engineering

The gate-all-around structure defines vertical nanowire transistors. It wraps gate material around the entire nanowire for better control. This design improves channel modulation and reduces short-channel effects in smaller transistors.

Contact Design

Contact engineering is vital in vertical nanowire transistors. Top and bottom contacts need careful design for efficient carrier movement. Advanced materials and techniques help minimize contact resistance. These improvements boost overall device performance.

Array Organization

Vertical fin-FET technology allows high-density integration through smart array organization. Tightly packed nanowire arrays achieve unprecedented transistor density on chips. This setup is crucial for realizing 3D device integration’s full potential.

| Feature | Benefit | Challenge |

|---|---|---|

| Gate-all-around structure | Enhanced electrostatic control | Complex fabrication process |

| Optimized contact design | Improved carrier transport | Material compatibility issues |

| Vertical fin-FET arrays | Higher transistor density | Precise alignment requirements |

These innovations lead to smaller, faster, and more efficient semiconductor devices. Ongoing research will refine device architecture further. We can expect exciting advancements in transistor design soon.

Performance Enhancement

Vertical nanowire transistors boost chip performance significantly. Their unique structure improves device density, power efficiency, and speed. These advancements lead to better electronic devices overall.

Density Benefits

The vertical design increases device density on chips. More transistors fit in the same area compared to traditional planar designs. This allows for more powerful and compact electronic devices.

Power Efficiency

Vertical nanowire transistors reduce leakage current, improving power efficiency. Their structure minimizes unwanted current flow when the transistor is off. This results in lower power consumption and longer battery life for mobile devices.

Speed Optimization

These transistors support high-frequency operation, essential for fast computing. The vertical design reduces parasitic capacitances, enabling quicker on-off switching. This speed boost enhances overall system performance in various applications.

| Feature | Benefit | Impact |

|---|---|---|

| Vertical Structure | Increased Device Density | More transistors per chip area |

| Nanowire Design | Leakage Current Reduction | Improved power efficiency |

| Optimized Carrier Transport | High-Frequency Operation | Faster computing speeds |

Integration Challenges

Vertical nanowire transistors promise advancements in 3D device integration. However, they face significant hurdles. Innovative solutions are needed to overcome obstacles in large-scale implementation.

Process Complexity

Vertical nanowire structures require intricate fabrication steps. Each stage can introduce errors, increasing process variability. Engineers must balance precision and cost-effectiveness for mass production viability.

Uniformity Control

Achieving array uniformity across large wafers is challenging. Vertically aligned nanowires must maintain consistent properties for reliable performance. Variations in size, spacing, or composition can lead to inconsistent electrical characteristics.

Yield Management

Defect density impacts overall yield in nanowire transistor production. Minimizing defects while maximizing output is crucial for commercial success. Advanced inspection methods are essential to identify issues early in manufacturing.

| Challenge | Impact | Mitigation Strategy |

|---|---|---|

| Process Complexity | Increased variability | Optimize fabrication steps |

| Array Uniformity | Inconsistent performance | Enhance growth control |

| Defect Density | Reduced yield | Implement advanced inspection |

Tackling these integration challenges is crucial. It will unlock the full potential of vertical nanowire transistors. This advancement will pave the way for next-generation electronic devices.

Characterization Methods

Vertical nanowire transistors need careful evaluation for top performance. Engineers use various techniques to analyze these devices. These include electrical testing, physical examination, and long-term reliability studies.

Electrical Testing

I-V characteristics are key in testing vertical nanowire transistors. They show device behavior under different voltage conditions. Engineers use special tools to plot current-voltage curves.

These plots reveal important details like threshold voltage and transconductance. Such data helps optimize transistor design and performance.

Physical Analysis

Electron microscopy is crucial for examining nanowire transistor structure. High-resolution imaging techniques like SEM and TEM are used. These methods let researchers see tiny details of nanowires.

They can observe nanowire size, gate setup, and material interfaces. This insight helps improve transistor design and manufacturing.

Reliability Assessment

Stress testing checks the long-term stability of vertical nanowire transistors. Devices undergo extreme conditions like high heat or voltage. This simulates fast aging and predicts device lifespans.

It also helps spot possible failure points. Recent research shows promising heat properties for silicon nanowire arrays. This suggests they could work well in thermoelectric applications.

| Characterization Method | Key Information Obtained | Equipment Used |

|---|---|---|

| I-V Characteristics | Current-voltage relationships, threshold voltage | Semiconductor parameter analyzer |

| Electron Microscopy | Nanowire dimensions, material interfaces | SEM, TEM |

| Stress Testing | Device lifetime, failure modes | Environmental test chambers |

Application Areas

Vertical nanowire transistors are changing tech domains. These tiny powerhouses excel in many applications. They’re used in advanced computing and cutting-edge sensing technologies.

Logic Integration

Vertical nanowires excel in logic circuits. They boost density and performance in microprocessors. This leads to more powerful and efficient computing systems.

These advancements push the limits of data processing. They also improve artificial intelligence capabilities.

Memory Devices

Vertically aligned nanowires are transforming memory tech. 3D NAND flash, built on these structures, offers amazing storage density. This allows for larger solid-state drives in smaller sizes.

Sensor Arrays

Vertical nanowire transistors create sensitive, compact sensor arrays. Gas sensors using these can detect tiny amounts of substances. This helps in environmental monitoring, industrial safety, and medical diagnostics.

These transistors also work in neuromorphic computing. This field mimics brain functions in hardware. It could revolutionize AI and machine learning.

| Application | Key Advantage | Example Use Case |

|---|---|---|

| Logic Integration | Higher density | Advanced AI processors |

| 3D NAND Flash | Increased storage capacity | High-capacity SSDs |

| Gas Sensors | Enhanced sensitivity | Industrial safety monitoring |

| Neuromorphic Computing | Brain-like processing | Next-gen AI applications |

Research continues to uncover new uses for vertical nanowire transistors. We’ll likely see more innovative applications across various industries soon.

Future Outlook

Vertical nanowire transistors are set to transform the semiconductor industry. These tiny structures offer exciting possibilities for device miniaturization and performance. The potential for scaling these technologies beyond current limits is remarkable.

Scaling Potential

Shrinking transistors while improving performance is crucial for advancing beyond-CMOS technologies. Vertical nanowire architectures allow for increased transistor density in a smaller footprint. This approach enhances functionality and paves the way for future innovations.

New Materials

Researchers are exploring novel materials to enhance nanowire transistors. III-V semiconductors, known for superior electron mobility, lead this innovation. These materials could boost device speed and efficiency significantly.

This breakthrough opens doors to new applications in high-performance computing and communications. The potential for advancing technology is immense.

Market Impact

Vertical nanowire transistors will disrupt the semiconductor market. Their applications range from advanced logic circuits to the growing emerging memory market. As these technologies mature, industry dynamics will shift.

Companies are racing to incorporate nanowire-based solutions into their product lines. This competition will drive further innovation and development in the field.