Interface trap density can greatly affect electronic component performance. In 2015, researchers found superconducting signals at 100 K in monolayered FeSe films. This discovery shows the importance of semiconductor interfaces in improving device efficiency.

Trap states at semiconductor interfaces can hurt electronic device performance. New research aims to reduce these trap densities. This work improves device efficiency and reliability.

Better detection methods and accurate calculations drive progress. These efforts help create cleaner and faster devices. Innovation in this field continues to grow.

Interface trap density shapes the future of many technologies. It affects electrification, information processing, and quantum computing. Understanding these tiny flaws is key to better device performance.

Mastering interface trap density can change the electronics industry. It unlocks the potential for superior devices. This knowledge paves the way for exciting technological advances.

Interface Trap Physics

Interface trap physics is vital for semiconductor device performance. It affects trap formation, energy band structure, and charge carrier interactions. These factors are key to improving device efficiency.

Formation Mechanisms

Traps form due to flaws at semiconductor-oxide interfaces. These defects create energy states that capture and release charge carriers. Lattice mismatches and dangling bonds influence this process.

Energy States

Interface traps change a semiconductor’s energy band structure. They add energy states within the bandgap, affecting electrical properties. The trap density impacts graphene field-effect devices significantly.

Charge Dynamics

Charge carriers interact with interface traps in complex ways. This affects device performance through trapping and detrapping. In some devices, inversion layer capacitance plays a minor role.

Understanding these dynamics is crucial for improving device efficiency and performance. Researchers use advanced models to study these interactions. They consider factors like thermal velocity and carrier cross-sections.

| Parameter | Value |

|---|---|

| Trap Density Range | 0.2 eV |

| Trap Density Height | 2×10^11 cm^-2eV^-1 |

| Thermal Velocity | 10^7 cm/s |

| Electron Cross Section | 1×10^-15 cm^2 |

| Hole Cross Section | 2.2×10^-16 cm^2 |

Studying these parameters helps researchers understand device behavior better. This knowledge leads to strategies that reduce interface trap effects. As a result, overall semiconductor performance can be enhanced.

Characterization Methods

Electrical characterization techniques are vital for understanding interface trap density. They offer valuable insights into device performance and reliability.

Electrical Techniques

Capacitance-voltage measurements are a powerful tool for analyzing interface traps. They reveal key parameters like trap densities and energy distributions.

Recent studies found interface state densities of 4×10^12 to 10^13 cm^−2 · eV^−1 in ferroelectric/dielectric stacks.

Capacitance Analysis

Detailed capacitance analysis provides critical data on device structure and performance. Recent advancements in high-speed electronics have shown impressive results.

Engineers observed accumulation capacitance values of 3.7 µF/cm² and minimum capacitance of 2.0 µF/cm² at low voltage. These findings help optimize device designs for better performance.

Spectroscopy

Deep-level transient spectroscopy offers unique insights into trap capture cross-sections and energy levels. It complements other techniques by providing a comprehensive view of interface defects.

Advanced methods like X-ray photoelectron spectroscopy further enhance our understanding of interface composition.

| Technique | Key Measurement | Typical Value |

|---|---|---|

| Capacitance-Voltage | Interface State Density | 4×10^12 – 10^13 cm^−2 · eV^−1 |

| Conductance Method | Minimum Interface Trap Density | 2.5 × 10^12 cm^−2·eV^−1 |

| Distributed Circuit Model | Border Trap Density | 1.5 × 10^19 cm^−3·eV^−1 |

Performance Impact

Interface traps significantly influence semiconductor device performance. They affect electron mobility, device stability, and long-term reliability. Understanding these impacts is crucial for designing robust devices for various applications.

Carrier Mobility

High trap densities reduce channel mobility in MOSFETs. This leads to lower current drive, affecting overall device performance. In low-temperature poly-silicon thin film transistors, deeper traps increase subthreshold swing and threshold voltage.

Device Stability

Interface traps cause threshold voltage shifts, impacting device stability. Positive interface trap charges can boost performance in doping-less nanowire-based devices. However, traps affect subthreshold slopes in InAs-nanowire-FETs and MOSFETs, influencing their stability.

Reliability

Interface traps contribute to hot carrier degradation, affecting device longevity. High-k dielectric materials like Al2O3 show promise in reducing thermal effects. However, they have higher trap densities compared to SiO2.

These traps can lead to charge trapping issues. This impacts the electrical and thermal characteristics of devices over time.

| Parameter | Impact of Interface Traps |

|---|---|

| Electron Mobility | Decreased channel mobility |

| Threshold Voltage | Increased shifts |

| Device Degradation | Accelerated hot carrier effects |

Researchers use advanced simulation techniques and trap models to study these effects. This approach helps in accurately predicting device behavior. It’s essential for developing next-generation semiconductor technologies.

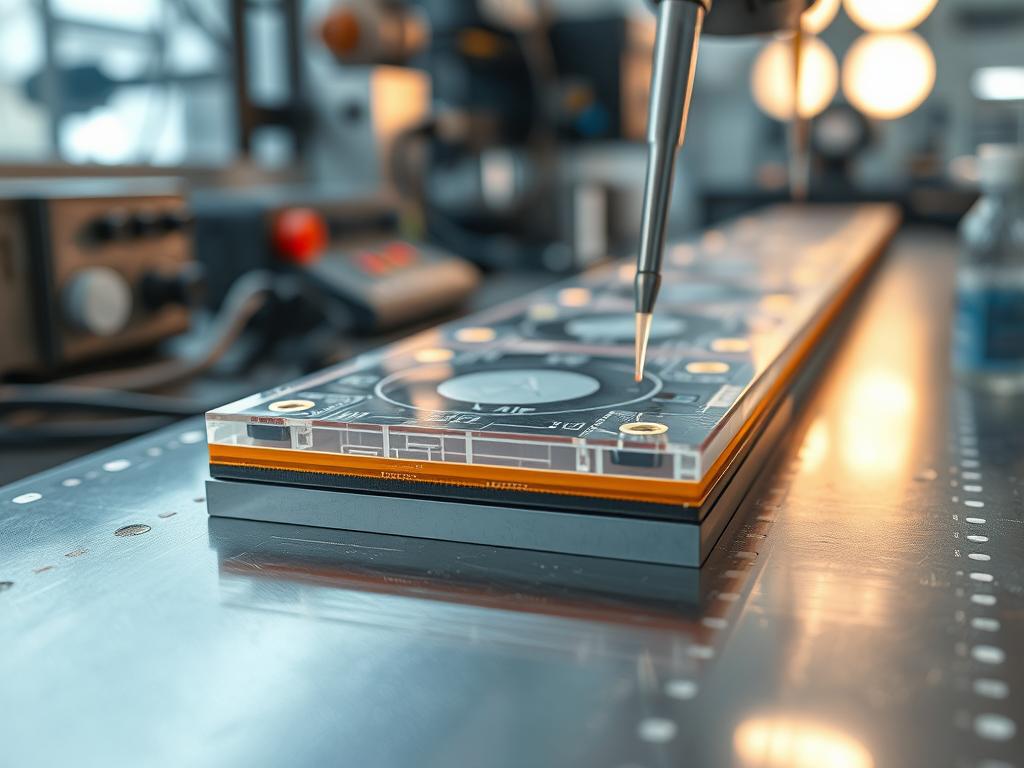

Process Optimization

Process optimization is vital for reducing interface trap density and boosting device performance. It focuses on key areas like fabrication control, surface treatments, and interface enhancement. These improvements significantly enhance the quality and efficiency of semiconductor devices.

Fabrication Control

Precise control of clean room processes is crucial for minimizing interface traps. Advanced techniques like hydrogen deuterium heat (HDH) treatment show promising results. This process compresses hydrogen gas at 70 atm and 200°C, effectively reducing interface traps.

Surface Treatments

Innovative surface passivation techniques are essential for enhancing device performance. Nitridation and hydrogen annealing have proven effective in reducing interface trap density. These treatments can improve device characteristics like short circuit current density and fill factor.

Interface Enhancement

High-k dielectrics have revolutionized interface enhancement in semiconductor devices. These materials offer superior electrical properties and better control over interface traps. In SiC MOSFETs, high-k dielectrics lead to lower on-resistance and higher blocking voltages.

| Parameter | Before Optimization | After Optimization |

|---|---|---|

| Average Efficiency (PERC) | 17.3% | 18.2% |

| Current Leakage | Base value | 0.5 orders decrease |

| Trapped Channel Electrons | 10% (>500 ns) | Reduced |

These optimization techniques have led to significant improvements in device performance. The average efficiency of PERC devices increased from 17.3% to 18.2% after HDH treatment. This demonstrates the effectiveness of these advanced fabrication processes.

Measurement Techniques

Accurate measurement of interface trap density is vital for semiconductor device performance. Advanced methods have improved our ability to quantify these traps. This has led to better device design and fabrication.

Advanced Methods

The conductance method and charge pumping technique are powerful tools for interface trap analysis. They offer high precision in determining trap densities across energy levels. A new method for accurately measuring interface trap in thin gate oxide layers has been developed.

Data Analysis

Interpreting measurement data requires complex analysis techniques. Researchers use modeling and simulation to extract meaningful parameters from raw data. Trap profiling algorithms map the distribution of traps across the semiconductor-oxide interface.

Validation

Ensuring accurate interface trap measurements is crucial. Scientists often use multiple techniques to cross-verify results. This multi-method approach helps identify and minimize systematic errors.

It leads to more robust characterization of interface trap properties.

| Method | Advantages | Limitations |

|---|---|---|

| Conductance Method | High sensitivity, energy-resolved measurements | Complex analysis, frequency-dependent |

| Charge Pumping Technique | Fast, spatial resolution | Limited to MOSFETs, bulk traps influence |

| Advanced Trap Profiling | Detailed energy distribution | Requires specialized equipment |

Advanced measurement techniques, rigorous data analysis, and validation procedures offer deep insights into interface trap behavior. These methods drive innovation in semiconductor technology. Researchers can now better understand and improve device performance.

Improvement Strategies

Cutting-edge strategies enhance semiconductor device performance. These methods target interface engineering, annealing techniques, and defect reduction. The goal is to boost efficiency and reliability.

Materials Engineering

Interface engineering is key to reducing trap densities. Engineers use buffer layers or new material combinations to lower interface defects. This approach improves device characteristics, especially in SiC MOSFETs with high interface trap density.

Thermal Processes

Annealing techniques passivate interface defects. The high-density hydrogen (HDH) treatment is a notable method. It compresses hydrogen gas at 70 atm and 200°C for one hour.

Research shows this technique enhances Si-H bonding. Fourier-transform infrared spectroscopy verifies these results.

Quality Control

Strict quality control maintains low trap density across wafers. Conductance-voltage measurements verify interface trap density. External quantum efficiency tests confirm conversion efficiency improvements at various wavelengths.

| Treatment | Before HDH | After HDH |

|---|---|---|

| Average Efficiency | 17.3% | 18.2% |

| Current Leakage | Higher | 0.5 orders decrease |

| Ideal Factor | Higher slope | Lower slope |

These strategies have led to significant advancements. HDH treatment increased PERC device efficiency from 17.3% to 18.2%. These gains highlight the importance of ongoing research.

Continued exploration of innovative semiconductor materials is crucial. Defect reduction techniques also play a vital role in improving performance.

Critical Applications

Interface trap density is vital in high-tech applications. It affects device performance in power electronics and advanced sensors. Let’s explore its influence on key technology areas.

High-Speed Devices

In power electronics, lower trap density enables faster switching and reduced losses. SiC MOSFETs offer lower on-resistance than Si MOSFETs at higher blocking voltages. This advantage comes from SiC’s critical electric field being ten times higher than Si.

As a result, SiC MOSFETs have a thousand-fold reduction in specific on-resistance. This makes them ideal for high-speed, high-power applications.

Memory

Interface traps greatly affect non-volatile memory technologies. They influence retention time and overall reliability of memory devices. Near-interface traps can capture about 10% of channel electrons for over 500 ns.

Sensors

CMOS image sensors are highly sensitive to trap-related noise. This noise impacts device performance and sensitivity. Conductance and capacitance measurements help characterize interface traps in MOS capacitors.

| Application | Impact of Interface Traps | Measurement Technique |

|---|---|---|

| Power Electronics | Affects switching speed and losses | I-V characteristic analysis |

| Non-volatile Memory | Influences retention time and reliability | Integrated-charge technique |

| CMOS Image Sensors | Causes noise, impacts sensitivity | Conductance and capacitance measurements |

Managing interface trap density is key to advancing critical applications. It’s crucial for pushing device performance and efficiency boundaries. As technology evolves, this phenomenon will remain a central focus.

Future Developments

The semiconductor industry is about to change dramatically. New technologies will transform how we manage interface trap density. We’re focusing on new materials and techniques to boost device performance.

New Materials

2D materials are leading this evolution with their unique properties. These thin layers, like graphene, could greatly reduce interface trap densities. They offer excellent control over electronic properties, potentially improving carrier mobility and reducing trap states.

Innovative Techniques

Advances in atomic-scale engineering allow precise interface manipulation. Researchers are exploring real-time monitoring of interface formation. These methods could provide key insights for optimizing fabrication and minimizing trap densities.

Trends

AI integration in semiconductor design is set to revolutionize the industry. Machine learning algorithms may predict and reduce interface trap formation. This could speed up the design process for high-performance devices.

Quantum computing is also expected to drive innovations in interface engineering. These developments will shape the future of next-generation electronics.